# Revolutionizing HPC Architecture

Advancing Energy Efficiency Through Next-Generation Interconnects and SoC Integration

**By: FNU Parshant**

### **HPC Market Growth**

# \$55.6B

# 100K+

#### Market Size by 2026

Projected global HPC market value, driven by scientific research and AI applications.

#### **Processing Cores**

Modern HPC systems can efficiently handle over 100,000 cores.

### Scalable Interconnects

Previous Gen

1

2

3

100 Gb/s speed

Millisecond latency

Current Gen

400 Gb/s speed

Sub-microsecond latency

Impact

4x improvement

Enables exascale computing

### Low-Power SoC Design

#### **Power Reduction**

Latest-generation designs show up to 75% reduction in power consumption.

#### **Performance Density**

Achieved up to 2.5 TFLOPS/mm<sup>2</sup>, a 3x improvement over discrete solutions.

#### Integration

Combines CPUs, GPUs, and FPGAs on a single chip for efficiency.

## **Advanced Packaging Technologies**

#### 3D Stacking

Overcomes traditional scaling limitations. Enables higher integration densities.

#### Chiplet Design

Allows for modular chip components. Improves yield and reduces costs.

# Integration Density Breakthrough

# **100M**

Transistors per mm<sup>2</sup> Achieved through advanced 3D packaging technologies.

## 40%

Density Increase Improvement over conventional 2D designs.

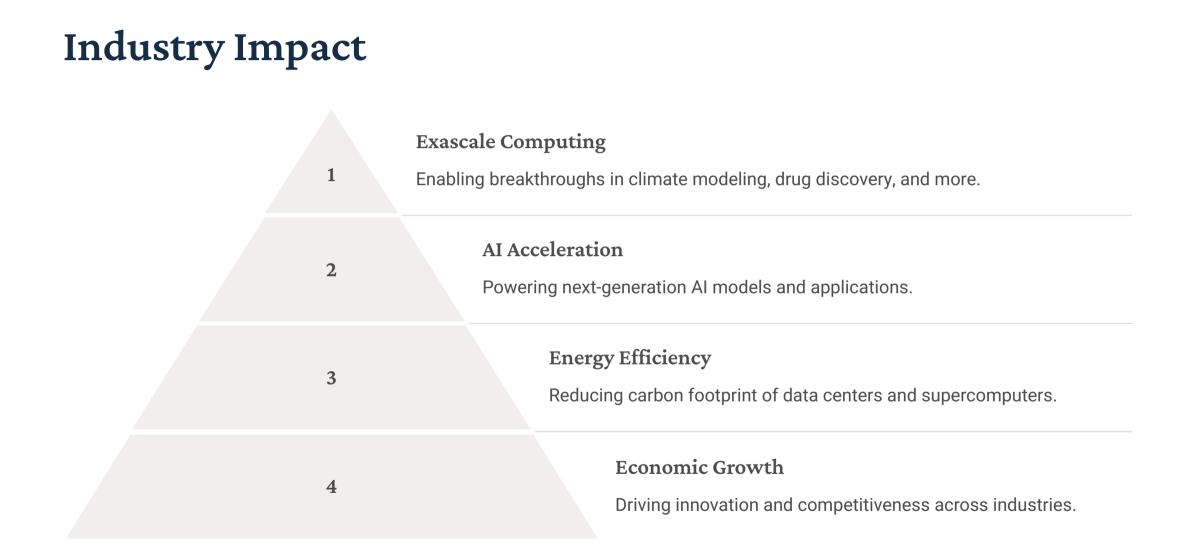

### **Next-Gen HPC Systems**

#### High Performance

Delivering exceptional computational power for complex workloads.

#### **Energy Efficiency**

Maintaining power envelope under 30 megawatts.

#### Scalability

Designed to handle growing demands of scientific and AI applications.

## **Real-World Applications**

# $\bigcirc$

#### AI Training

Enabling complex simulations and data analysis in physics, chemistry, and biology.

Scientific Computing

Accelerating machine learning model training for advanced AI applications.

# oOO

#### Data Analytics

Processing massive datasets for business intelligence and research insights.

### **Performance Improvements**

60%

**3**x

Performance-per-Watt Gain

Improvement compared to previous HPC architectures. **Computational Density**

Increase in FLOPS per unit area over traditional solutions.

## **Challenges and Future Directions**

#### Thermal Management

Developing advanced cooling solutions for high-density chips.

#### Interconnect Scaling

2

3

Pushing data transfer speeds beyond 1 Tb/s while reducing latency.

#### Software Optimization

Creating tools to fully utilize heterogeneous computing resources.

### **Conclusion:** The Future of HPC

#### **Continued Innovation**

Pushing boundaries in interconnects, SoC design, and packaging technologies. Sustainable Computing

Balancing performance gains with energy efficiency improvements.

3 Collaborative Research

Fostering partnerships between academia, industry, and government labs.

### Thank You