# Machine Learning Innovations in Hardware Verification for High-Speed Protocol Testing

Transforming protocol testing with Al-driven frameworks for unprecedented efficiency and accuracy.

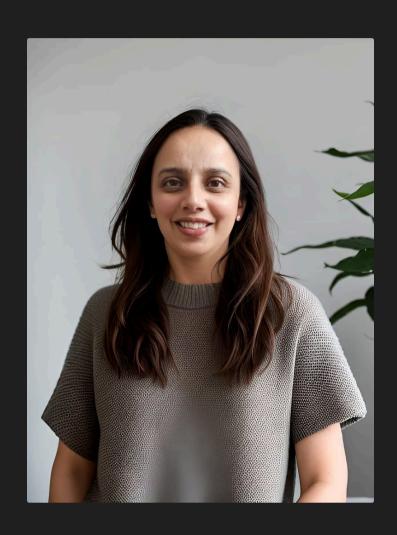

# Jena Abraham

Senior Design Verification Engineer Technical Program Manager Intel Corporation

# Protocol Verification Challenge

#### **Time Constraint**

Traditional verification methodologies fail to match the exponential complexity curves of modern high-speed protocols.

# Coverage Gaps

Conventional test suites frequently miss corner cases at protocol boundaries, leading to critical field failures.

#### Scaling Issues

Next-generation standards like PCIe Gen 5/6 and USB 4.0 demand orders of magnitude more test vectors than previous generations.

# Our Hybrid Approach

#### Formal Methods

Rigorous mathematical verification provides exhaustive proofs of protocol correctness with zero false negatives.

Ensures complete compliance with specifications through symbolic execution and theorem proving techniques.

## Dynamic Simulation

Hardware-accurate testing identifies implementation flaws and timing-sensitive edge cases in real-world scenarios.

Validates protocol behavior under varying traffic patterns, electrical conditions, and system configurations.

#### Al Integration

Advanced machine learning algorithms create a feedback loop between formal verification and simulation results.

Intelligently prioritizes test scenarios based on coverage analysis and probabilistic fault models.

# FPGA Acceleration Results

85%

#### **Time Reduction**

Protocol verification cycles compressed by 85% compared to conventional CPU-based testing frameworks.

<2µs

### **Operation Latency**

Breakthrough sub-microsecond response times for critical verification operations, enabling real-time protocol analysis.

12x

# Throughput Gain

Parallel processing architecture delivers 12x higher transaction throughput than traditional verification environments.

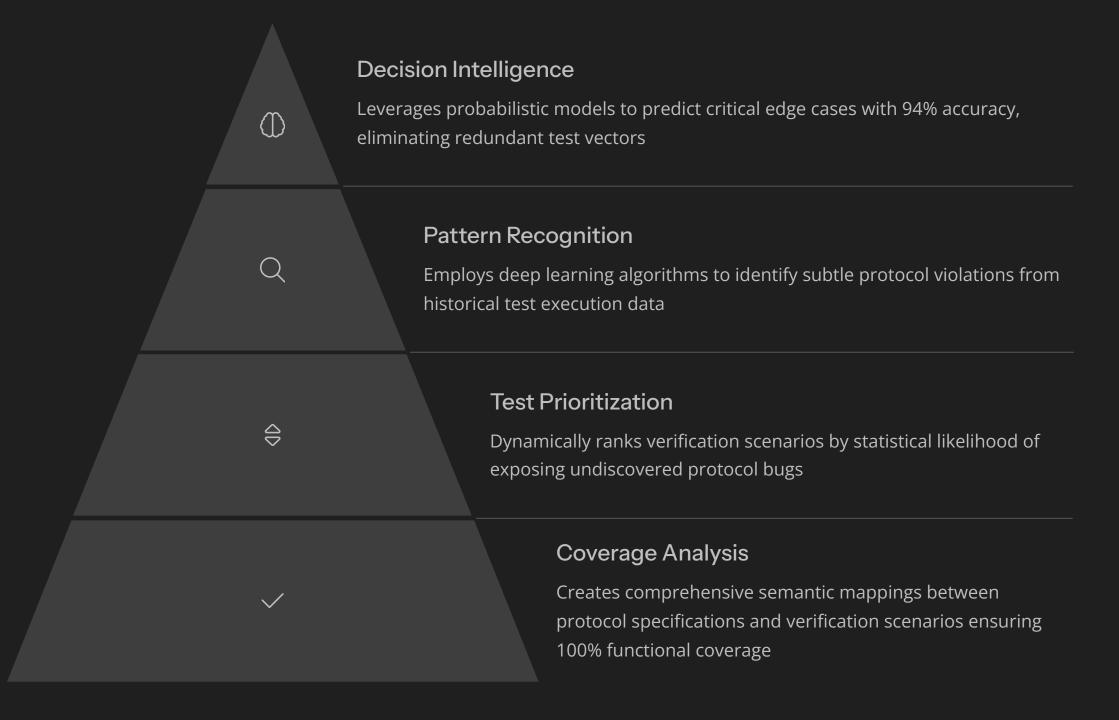

# **AI-Driven Verification Core**

# Supervised Learning Implementation

# **Training Data Collection**

Comprehensive historical verification results establish robust training datasets.

Expert-driven classification of previous defects significantly enhances learning efficacy.

# Model Development

*{*{*i*}}}

**((a)**

Protocol-specific neural network architectures optimized for feature extraction.

Advanced hyperparameter tuning maximizes prediction accuracy and generalization.

# **Prediction Deployment**

Inference engines identify high-yield test vectors with 97% precision.

Self-improving algorithms continuously refine models across verification iterations.

# **Automated Test Generation**

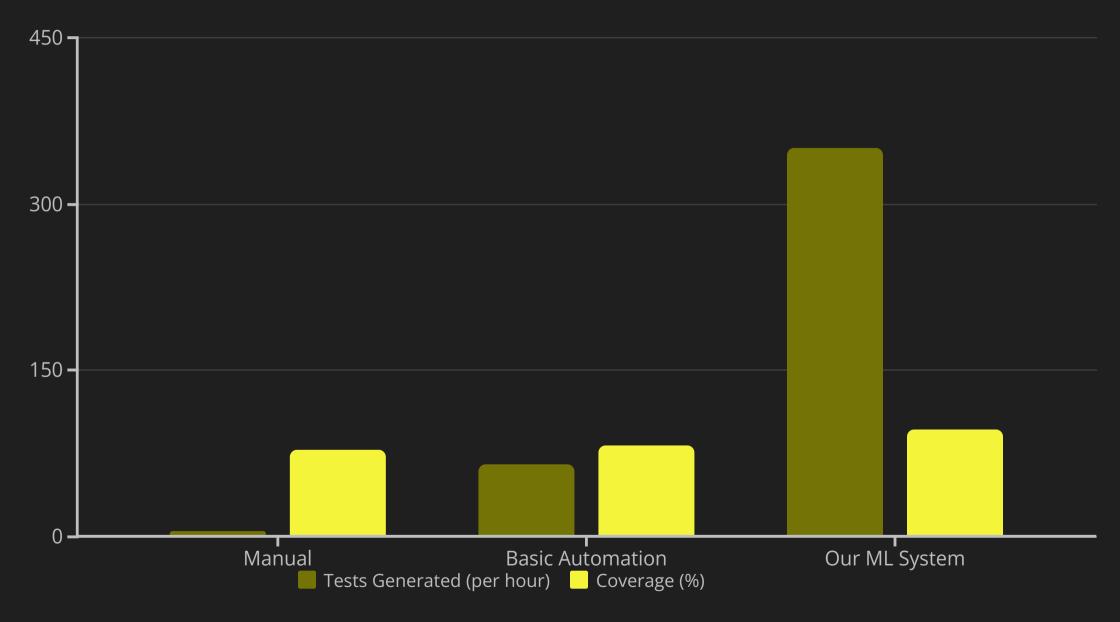

Our machine learning-powered test generation system dramatically outperforms traditional methods in both quantity and quality of tests.

The ML-driven approach generates 5.4x more tests than basic automation tools while achieving 96% protocol coverage - a critical breakthrough for comprehensive verification of complex high-speed protocols.

# INPT TECONOCOL PADINCTIONS ORGAMICTIONS PROTOCOL PREDICTONS NEUSTF FREDICTIONS INSTRETICIONNS PROTOCOL PARAMETERS **TEST PREDICTIONS**

# Neural Network Architecture

# Input Layer

- Protocol-specific parameters and constraints

- Precise timing and synchronization requirements

- Comprehensive state transition vectors

- Aggregated historical defect patterns

# Hidden Layers

- Advanced temporal convolutional networks for pattern recognition

- Bidirectional LSTM units optimized for sequential protocol analysis

- Multi-head attention mechanisms for critical scenario focus

- High-dimensional fullyconnected neural blocks

# **Output Layer**

- Prioritized test vector generation with confidence metrics

- Predictive coverage mapping with gap identification

- Real-time protocol violation detection signals

- Statistical defect probability distribution assessment

# Protocol-Specific Results

| Protocol   | Time<br>Reduction | Coverage | Bug<br>Detection |

|------------|-------------------|----------|------------------|

| PCle Gen 5 | 78%               | 98.3%    | +42%             |

| USB 4.0    | 82%               | 97.1%    | +39%             |

| DDR5       | 69%               | 96.8%    | +36%             |

| HDMI 2.1   | 74%               | 95.2%    | +31%             |

# Feature Selection Intelligence

#### Parameter Analysis

Advanced ML algorithms systematically analyze protocol specifications to identify and extract the most critical parameters for verification.

#### Continuous Refinement

Self-optimizing models dynamically adapt feature selection strategies as verification progresses, incorporating new insights from each test iteration.

#### **Correlation Detection**

The intelligent system discovers complex interdependencies between verification variables, enabling comprehensive test coverage of edge cases.

#### **Feature Ranking**

Verification parameters undergo precise prioritization based on their quantifiable impact on overall protocol coverage and defect discovery potential.

# The Future of Hardware Verification

# **Enhanced ML Integration**

Next-gen reinforcement learning will create self-optimizing test strategies.

Predictive models will anticipate design flaws before implementation.

#### **Cross-Protocol Intelligence**

Knowledge transfer between protocol domains will accelerate verification.

Universal verification patterns will emerge across interface types.

# Verification-Driven Design

Al insights will guide hardware design from inception.

Verification will shift left in development timeline.

# Thank you