# Adaptive Power Calculation for Battery-Operated Chip Design

Battery-powered devices demand meticulous power optimization throughout the design lifecycle. Our innovative adaptive methodology dynamically recalibrates power calculations in real-time, dramatically enhancing efficiency across both active operation and idle states. This breakthrough approach leads to extended battery life without compromising performance.

By: Puneet Gupta

# The Power Calculation Challenge

#### Dynamic Parameters

Activity factors, parasitic capacitances, and resistance values constantly shift throughout the design process, creating a perpetually moving target for accurate power estimation.

### Early Inaccuracies

Initial power estimations

frequently neglect critical

variables, triggering cascading

design errors that compound over

time and become increasingly

costly to rectify.

# Distribution Network Issues

Power delivery networks based on flawed baseline calculations introduce significant reliability vulnerabilities, potentially leading to catastrophic device failures under real-world operating conditions.

# Current State: Fixed Calculations

ı

#### **Initial Estimations**

Power budgets established on preliminary specifications with significant margin for error

2

### Static Design Parameters

Minimal recalibration despite continuous influx of critical design data

3

### Late-Stage Detection

Power inefficiencies identified during validation necessitate expensive and time-consuming redesigns

4

## Suboptimal Results

Finished devices operate with compromised battery longevity or reduced feature capabilities

# Introducing Adaptive Methodology

#### Calculate

Generate comprehensive power estimates using preliminary specifications and statistical models

#### Validate

Benchmark against previous iterations to quantify efficiency improvements and confirm design targets

#### Integrate

Dynamically incorporate real-time measurement data and refined parameters throughout development

### Adjust

Recalibrate power specifications with enhanced precision to optimize battery performance

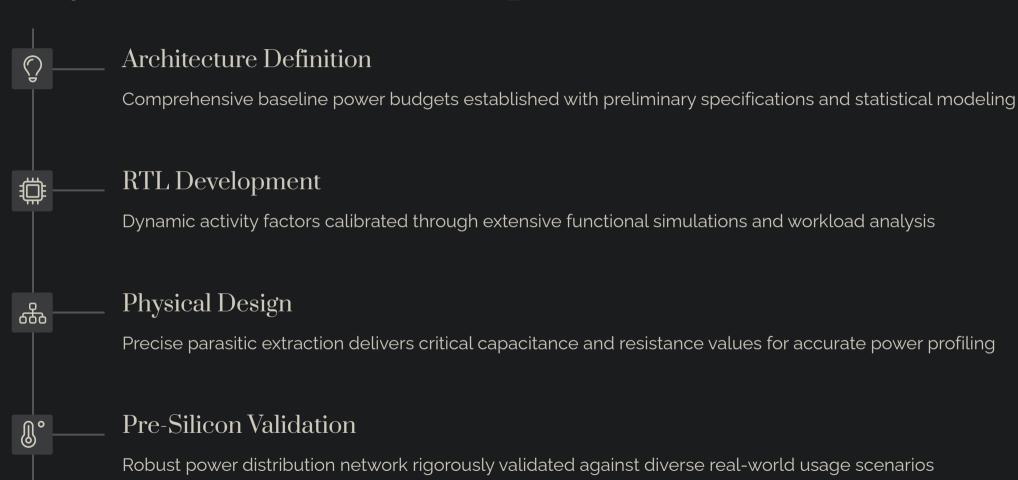

# Key Milestones for Adaptive Recalculation

# Tracking Input Quality

Quality metrics improve significantly across the design process, enabling more accurate power calculations at each stage.

### Early RTL Phase

Activity Factor Certainty: 45%

Parasitic Data Completeness: 20%

Capacitance Measurement Accuracy: 30%

# Synthesis Phase

Activity Factor Certainty: 65%

Parasitic Data Completeness:

55%

Capacitance Measurement Accuracy: 60%

#### Place & Route Phase

Activity Factor Certainty: 80%

Parasitic Data Completeness:

85%

Capacitance Measurement Accuracy: 90%

### Final Design Phase

Activity Factor Certainty: 95%

Parasitic Data Completeness:

98%

Capacitance Measurement Accuracy: 97%

# Automation Strategy

### Dynamic Scripts

- Intelligently identify

available input parameters

at each design stage

- Implement optimal calculation models based on data maturity

- Proactively flag missing critical data with severity classifications

#### Predictive Models

- Bridge information gaps using machine learning estimations

- Leverage historical patterns from previous chip designs

- Self-optimize prediction accuracy with each design iteration

### Cross-Team Integration

- Real-time notification system for power specification changes

- Seamless API connections to industry-standard design tools

- Comprehensive power analytics dashboards with trend visualization

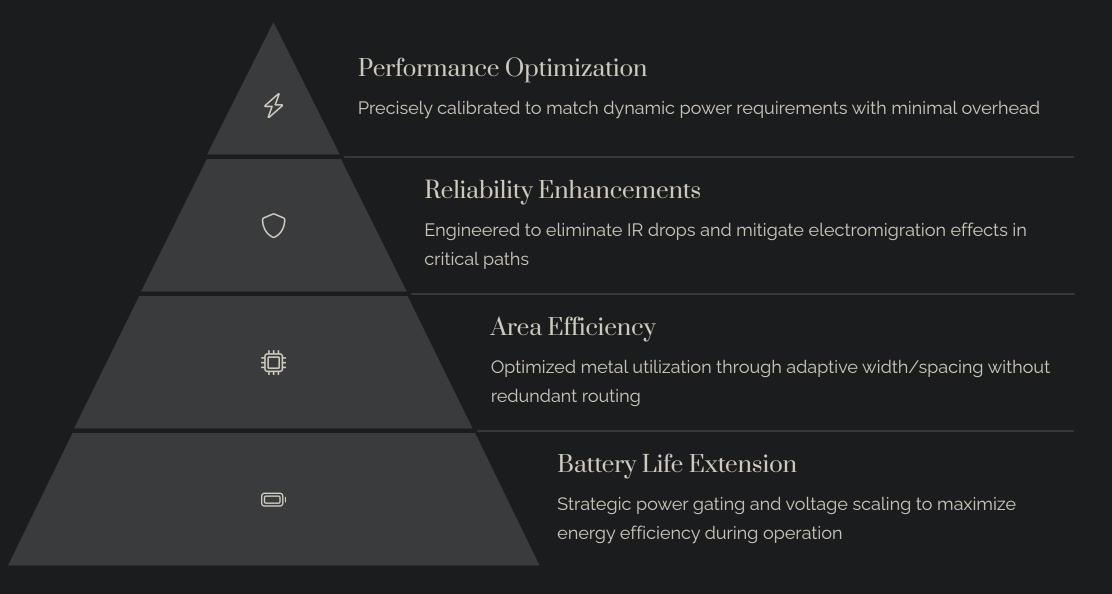

# Power Distribution Network Optimization

# Real-World Results

37%

Power Savings

Significant reduction in active mode power consumption, enabling more efficient chip operation

42%

Design Efficiency

Dramatic decrease in redesign cycles, accelerating time-to-market while reducing development costs

2.8x

Battery Longevity

Substantial extension in operational runtime compared to previous generation designs

# Implementation Roadmap

#### **Tool Integration**

Seamlessly integrate adaptive power calculation with existing EDA infrastructure for frictionless adoption

#### Process Updates

Implement strategic design checkpoints to trigger automated power recalculation based on data quality thresholds

### Team Training

Equip engineering teams with comprehensive understanding of adaptive methodologies and practical implementation techniques

### Continuous Improvement

Systematically refine prediction models using realworld power measurements to enhance accuracy with each design iteration

# Key Takeaways

#### Adaptive > Static

Dynamic power calculation

methodologies significantly outperform

fixed approaches throughout the

design lifecycle. Static methods

inevitably lead to performance

compromises and potential thermal

failures.

### Data-Driven Design

Comprehensive input quality tracking enables transparent, confidence-based decision-making. Engineers can precisely evaluate reliability levels for each calculation, ensuring informed design choices.

#### Automation Imperative

Intelligent algorithms and ML-based predictive models eliminate human error in repetitive recalculations.

Seamless integration with established EDA workflows dramatically accelerates team adoption and implementation.

Thankyou