# Backside Power Delivery: Revolutionizing Chip Design

Backside power delivery network (BSPDN) technology represents a revolutionary advancement in semiconductor design, addressing critical power distribution challenges in advanced process nodes. This architectural innovation separates power delivery from signal routing through vertical integration, enabling significant improvements in chip performance and efficiency.

The approach incorporates nano-Through Silicon Vias for direct power delivery through thinned silicon substrates, dramatically reducing routing congestion and IR drop while enhancing signal integrity. Intel's PowerVia implementation, alongside developments from other major semiconductor manufacturers, demonstrates the technology's potential to transform power delivery architectures.

#### By: Ramalinga Reddy Kotapati

## **Traditional Power Delivery Limitations**

4

#### **Routing Congestion**

In advanced 5nm process nodes, power delivery infrastructure consumes nearly 40% of available routing resources. As metal pitch scales down to 24nm, IR drop increases dramatically by 45% compared to previous technology nodes, severely constraining signal routing options.

#### Voltage Degradation

Modern chips operating at reduced voltages of 0.7V experience significant voltage drops of 12-15% across the die during high computational loads. In critical corner cases, these drops can spike to 16.5%, pushing transistors toward their operational margins.

#### Power Supply Noise

Dynamic circuit operation generates substantial power supply noise reaching 85-95mV peak-to-peak under typical workloads. The PDN's frequencydependent impedance fluctuates by up to ±22% from nominal values, compromising signal integrity and timing predictability.

## **BSPDN Architecture: A Revolutionary Approach**

#### **Wafer Processing**

Precision substrate thinning to 12-15µm thickness with exceptional warpage control maintained within 45µm across 300mm wafers. Advanced nano-TSV fabrication achieves remarkable aspect ratios of 10:1, featuring ultra-fine via diameters of 100-200nm and precise depths extending to 2.5µm.

#### **Power Layer Implementation**

Specialized backside metal stack utilizing advanced copper metallization techniques achieves ultra-low sheet resistance of 0.015Ω/□. The engineered three-layer power distribution network with optimized 4.2µm thickness delivers substantial 58% reduction in PDN impedance compared to conventional approaches.

#### **System Benefits**

Significant reduction in required metal layers from conventional 10-12 down to just 7-8 for functionally equivalent designs. Average signal interconnect length decreases by 25%, directly contributing to dramatic RC delay improvement of 35% while simultaneously reducing signal crosstalk by 42%.

## Performance Comparison: Traditional vs. BSPDN

| Parameter                    | Traditional PDN | BSPDN Technology |

|------------------------------|-----------------|------------------|

| Wire Resistance (5nm vs 7nm) | 150%            | 100%             |

| Power Consumption (W/mm²)    | 2.5             | 1.75             |

| Metal Layer Usage (%)        | 35              | 15               |

| PDN Resistance (Normalized)  | 100%            | 55%              |

| IR Drop (Normalized)         | 100%            | 45%              |

| Required Metal Layers        | 8               | 3                |

## Manufacturing Considerations

Wafer Thinning

Ultra-precise thinning to 5-10µm with exceptional surface integrity below 2nm RMS roughness

<u>þ</u>

\*\*\*\*

#### **TSV Integration**

High-precision 500nm TSVs featuring industry-leading 10:1 aspect ratios with near-vertical 89.8° ±0.2° sidewall profiles

ß

#### **Thermal Management**

Strategic TSV placement architecture reduces critical thermal gradients by 40%, enhancing device reliability

State-of-the-art chemical-mechanical planarization preserves structural integrity while limiting wafer bow to under 40µm. Advanced copper electroplating delivers defect-free TSV filling with minimal stress-induced carrier mobility variation (below 1.5%). Next-generation thermal interface materials with superior conductivity (>10 W/mK) effectively maintain junction temperatures under 80°C even at extreme power densities of 3.2W/mm<sup>2</sup>.

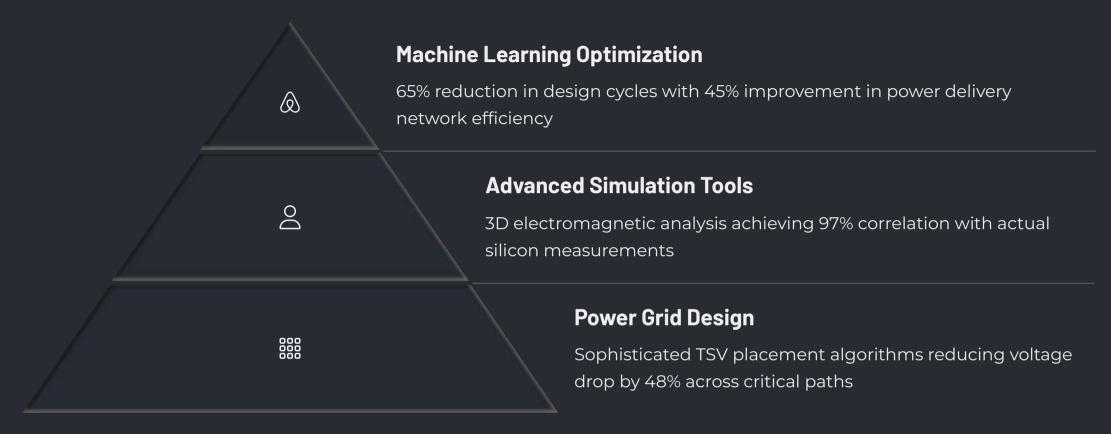

# **Design Methodology Adaptation**

Leading-edge design platforms have evolved to address the unique challenges of 3D power delivery networks. Enhanced thermal simulation capabilities now handle intricate three-dimensional structures with remarkable temperature prediction accuracy within 2°C of measured data throughout the entire die surface.

State-of-the-art current density analysis tools support comprehensive full-chip simulations at unprecedented grid resolutions of 25nm, enabling engineers to precisely anticipate electromigration vulnerabilities. These advancements have delivered a substantial 70% improvement in verification runtime efficiency compared to conventional methodologies, significantly accelerating time-to-market.

## **Industry Adoption: Major Players**

### Intel PowerVia

Pioneering 18A node implementation achieving 30% power delivery efficiency enhancement. Features advanced 10µm wafer thinning technology with superior 2.8A/mm<sup>2</sup> current density capacity while maintaining precise ±4% voltage regulation across the die.

### TSMC

Strategic \$2.8 billion R&D investment in backside power delivery architecture. Production-ready prototypes demonstrate exceptional 28% power efficiency gains coupled with 15% performance improvements, scheduled for full integration in upcoming N2 (2nm) process node.

#### Samsung

Breakthrough vertical power delivery system utilizing ultra-precise 150nm diameter TSVs with industry-leading 10:1 aspect ratios. Advanced metallization techniques yield 2.2x electromigration resistance compared to traditional power delivery architectures.

## **Future Prospects: 2025 and Beyond**

#### **Market Adoption**

High-performance computing and mobile application processors incorporating BSPDN by 2025

#### **Market Opportunity**

Projected market value for BSPDN technology integration across semiconductor sectors

#### **Efficiency Improvement**

Anticipated power efficiency gains in next-generation chipsets utilizing advanced BSPDN architectures

**Current Density**

Projected peak current handling capacity while maintaining precise ±3.5% voltage regulation

Advanced research initiatives are now accelerating toward breakthrough BSPDN implementations with unprecedented specifications. Elite engineering teams are developing ultra-miniaturized TSV structures with diameters below 100nm and revolutionary 12:1 aspect ratios. Complementary thermal management innovations promise to dramatically reduce junction temperatures by up to 10°C beyond current implementations, paving the way for the next generation of high-performance, energy-efficient computing platforms.

### **Performance Metrics Across Manufacturers**

#### Power Efficiency Improvement

Intel leads with 30% improvement, followed by TSMC at 28% and Samsung at 25% with their backside power delivery implementations.

#### **TSV Yield Rate**

Intel achieves highest manufacturing precision with 99.95% TSV yield rate, while TSMC and Samsung follow closely at 99.8% and 99.7% respectively.

#### Current Density (A/mm<sup>2</sup>)

PowerVia technology enables Intel to reach 2.8A/mm<sup>2</sup>, outperforming Samsung's 2.6A/mm<sup>2</sup> and TSMC's 2.5A/mm<sup>2</sup> implementations.

#### **Temperature Reduction**

All manufacturers achieve significant cooling benefits, with Intel reducing temperatures by 8°C while TSMC and Samsung both achieve 7°C reductions.

The comparison illustrates key performance metrics across major semiconductor manufacturers implementing backside power delivery technology. Intel currently leads in most categories with their PowerVia implementation, while all manufacturers are achieving significant improvements in power efficiency, thermal management, and current handling capabilities.

## Future Implications: A Crucial Scaling Knob

#### **Density Improvement**

BSPDN implementations achieve transistor density improvements of up to 25% compared to traditional power delivery architectures at equivalent technology nodes, by reducing power routing overhead that typically consumes 35-40% of metal layer resources.

#### Performance Enhancements

Overall power efficiency improvements of 22-25% with dynamic power reduction reaching 30% in high-performance computing. Signal integrity measurements show 35% reduction in power supply induced jitter, enabling reliable operation at data rates up to 90 Gbps.

#### **Design Flexibility**

Separation of power and signal domains enables 30% reduction in routing complexity with average wire length reductions of 20-25%. Required metal layers reduced from 10-12 to 7-8 for equivalent functionality, contributing to path delay reductions of up to 18%.

## **Economic Impact and Conclusion**

Backside power delivery network technology represents a revolutionary advancement in semiconductor manufacturing, delivering dramatic improvements in power efficiency, thermal performance, and signal integrity. The technology's strategic advantages—including significantly higher transistor density and reduced routing complexity—outweigh the initial cost premium, particularly as manufacturers scale below 2nm.

With Intel, TSMC, and Samsung all committing substantial resources to BSPDN implementation, the technology has emerged as an essential scaling mechanism for next-generation computing. As design methodologies mature and manufacturing processes stabilize, backside power delivery will become the standard architecture for high-performance, energy-efficient chips across mobile, AI, and data center applications.

## Thankyou