# Advances in Physical Design for Next-Gen FinFET and GAA

The semiconductor industry is evolving rapidly with FinFET and Gate-All-Around (GAA) technologies. These advancements are revolutionizing chip design, offering improved performance, power efficiency, and density.

By: Ramalinga Reddy Kotapati

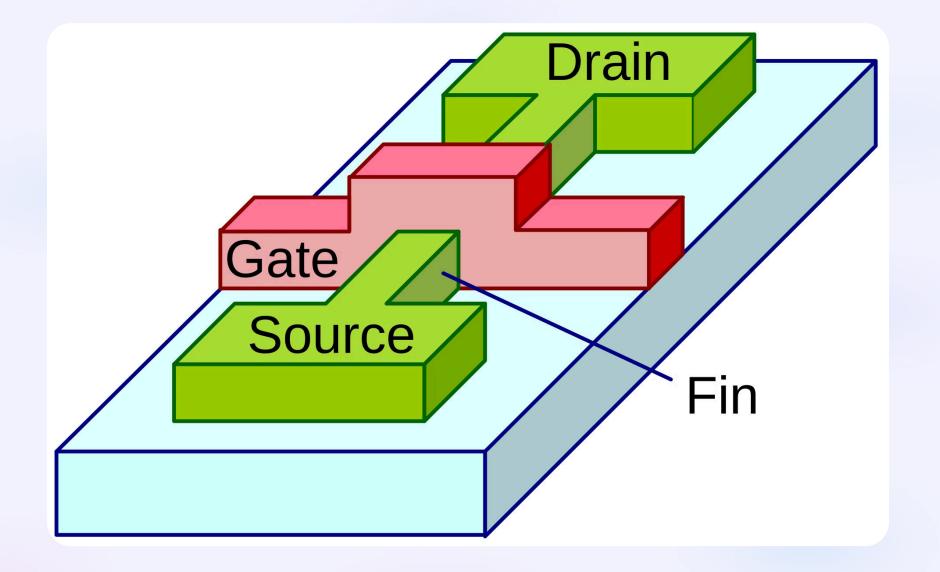

#### FinFET

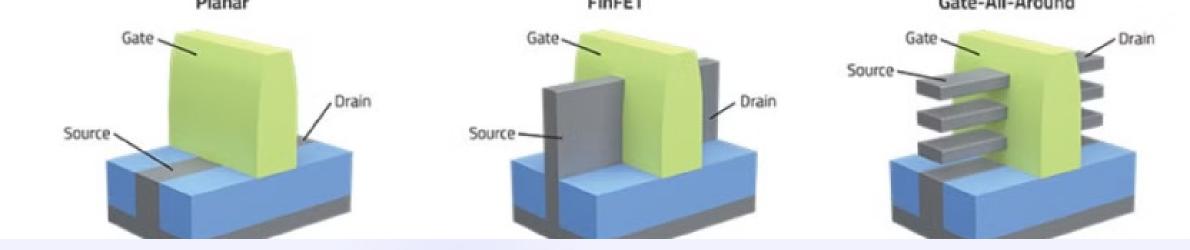

A fin field-effect transistor (FinFET) is a <u>multigate device</u>, a <u>MOSFET</u> (metal-oxide-semiconductor <u>field-effect transistor</u>) built on a <u>substrate</u> where the gate is placed on two, three, or four sides of the channel or wrapped around the channel (gate all around), forming a double or even multi gate structure. These devices have been given the generic name "FinFETs" because the source/drain region forms fins on the silicon surface. The FinFET devices have significantly faster <u>switching times</u> and higher <u>current density</u> than planar <u>CMOS</u> (complementary metal-oxide-semiconductor) technology.

### GAA

Gate-all-around FET (GAA FET) is a modified transistor structure where the gate contacts the channel from all sides. It's basically a silicon nanowire with a gate going around it. In some cases, the gate-all-around FET could have InGaAs or other III-V materials in the channels.

Introduced by major foundries around the 3nm/2nm nodes when further scaling of finFET devices became untenable due to issues such as channel width variations, the approach allows for the vertical stacking of planar channels, leading to a notable increase in the effective channel width. By stacking these planar channels vertically, the effective channel width is increased, resulting in increased device drive current capability with less leakage, reduced power consumption, and enhanced performance. However, the unique structure of GAA transistors make design, metrology, inspection, and test significantly more challenging and expensive.

### **Evolution from FinFET to GAA**

### **FinFET Introduction**

FinFETs emerged to overcome planar transistor limitations. They offered better electrostatic control and reduced leakage current.

#### **FinFET Optimization**

2

3

Continuous improvements in FinFET design led to enhanced performance and scalability. Multi-fin structures became common.

#### GAA Development

GAA technology evolved to address FinFET scaling challenges. It provides superior channel control and enables further miniaturization.

### Impact on Physical Design Requirements

#### Layout Complexity

GAA structures demand more sophisticated layout techniques. Design rules become increasingly complex and numerous.

#### Interconnect Challenges

Reduced metal pitches require advanced routing strategies. Via optimization becomes critical for performance and yield.

#### **Power Distribution**

Efficient power delivery networks are crucial. IR drop and electromigration concerns necessitate careful planning.

### Advanced EDA Tools

### Machine Learning Integration

Al-powered tools optimize layout and predict design issues. They accelerate convergence and improve quality of results.

### Multi-Patterning Aware

EDA tools handle complex multi-patterning decomposition. They ensure manufacturability while maximizing design density.

### 3D-IC Design Support

3

Tools now accommodate 3D integration challenges. They manage through-silicon vias and die-to-die interfaces effectively.

2

### **Design Strategies for Advanced Nodes**

### Standard Cell Optimization

Customized standard cells leverage GAA capabilities. Track height reduction and pin access optimization are key focus areas.

#### **Clock Tree Synthesis**

Advanced CTS techniques minimize skew and latency. Hybrid clock mesh-tree structures become more prevalent.

### Signal Integrity Management

Crosstalk analysis and mitigation are critical. Shielding and buffer insertion strategies are refined for GAA nodes.

#### **DFM Integration**

Design for manufacturability is integrated earlier. Lithography simulation and layout dependent effects are considered during physical design.

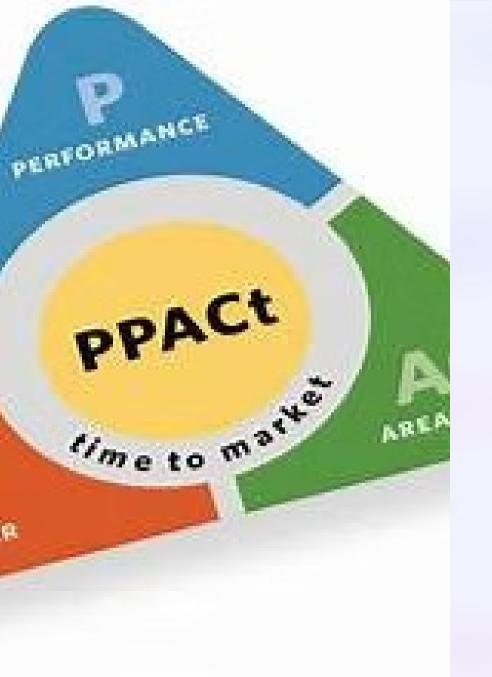

## Power, Performance, and Area (PPA) Improvements

| Metric      | FinFET   | GAA  | Improvement |

|-------------|----------|------|-------------|

| Power       | Baseline | -20% | 20%         |

| Performance | Baseline | +15% | 15%         |

| Area        | Baseline | -30% | 30%         |

### **Challenges in High-Density Chip Design**

### **Thermal Management**

Higher transistor density increases power density. Advanced cooling solutions and thermal-aware placement become essential.

### Variability Control

1

2

3

Process variations impact device performance more severely. Statistical design techniques and adaptive circuits gain importance.

### **Yield Optimization**

Defect sensitivity rises with scaling. Redundancy schemes and error correction techniques are critical for yield improvement.

### **High-Speed Design Considerations**

### **Clock Distribution**

Minimizing clock skew is crucial. Resonant clocking and optical clock distribution are explored.

### all

#### Signal Integrity

Managing crosstalk and noise becomes more challenging. Advanced shielding and equalization techniques are employed.

### 鬯

### **On-Chip Communication**

High-speed SerDes and Network-on-Chip architectures are optimized. They enable efficient data movement within the chip.

### **Future Directions in Physical Design**

### **3D Integration**

Vertical integration will become more prevalent. Tools will evolve to handle complex 3D structures and thermal management.

### **Quantum Computing**

Physical design tools will adapt for quantum circuits. Cryogenic electronics and qubit layout will present unique challenges.

### Neuromorphic Design

Brain-inspired architectures will require new design paradigms. Analog/mixedsignal integration will become more important.

### **Conclusion: The Road Ahead**

2

Continued Scaling

1

GAA technology will enable further transistor scaling. Physical design tools will evolve to meet new challenges. AI-Driven Design

Machine learning will play a larger role in chip design. Automated design space exploration will become more sophisticated. 3

#### Heterogeneous Integration

Diverse technologies will be combined on a single package. Physical design will extend beyond the chip to system-level optimization.

### **Thank You**