# Edge-Ready GenAI: Engineering Low-Latency Solutions for ResourceConstrained Environments

Welcome to our comprehensive exploration of generative AI deployment in resource-constrained environments. As enterprises increasingly demand real-time AI capabilities, understanding how to optimize GenAI for edge computing becomes critical for developers and engineers.

Today we'll examine systematic approaches to maintain performance while significantly reducing computational demands, energy consumption, and latency—opening new possibilities for intelligent edge applications.

By: Sai Kalyan Reddy Pentaparthi

#### About me:

#### Sai Kalyan Reddy Pentaparthi

**Principal Engineer Software**

ST Engineering iDirect, Inc.

Working on enhancing connectivity through Global IP-Satellite Network Infrastructure

www.linkedin.com/in/saikalyanrp

## The Edge Computing Frontier

#### **Limited Computational Resources**

Edge devices generally have limited processing power, memory, and storage compared to centralized cloud systems.

#### **Energy Constraints**

Many edge devices run on batteries or operate under strict power limits, restricting AI model complexity.

#### **Connectivity Challenges**

Edge AI solutions must operate reliably even with limited or no connection to cloud resources.

#### Real-time Requirements

Applications often require low-latency responses, increasing performance demands on edge models.

## **Edge Al Market Trends**

#### • Strong Market Expansion:

- The Edge AI accelerator market is growing rapidly with a 38.9%

CAGR.

- It is projected to reach \$7.68 billion by 2027, showing strong demand for on-device AI.

#### • Key Adoption Drivers:

- The need for low latency (78.3% of organizations) to ensure realtime responses is a primary driver.

- **Data privacy concerns (64.7%)** also encourage local AI processing.

- Industry Adapting to Challenges:

- Model optimization (used in 82% of deployments) is widely applied to run complex AI efficiently on constrained edge hardware.

## The Edge Al Market Evolution

**Current State** Limited GenAI deployment at edge due to resource constraints **Next 12 Months** Increasing adoption of optimized edge AI solutions 18-24 Months 3 Most enterprises requiring real-time edge AI capabilities Beyond 2025 Ubiquitous edge AI with specialized hardware acceleration

Market forecasts indicate we're at an inflection point in edge AI adoption. The next 18-24 months will witness a dramatic shift as enterprises increasingly require real-time AI capabilities without the latency penalties of cloud-dependent architectures.

This transition is being accelerated by advances in hardware acceleration, model optimization techniques, and the growing necessity for privacy-preserving local computation.

## **Edge Al Market Trends**

#### • Strong Market Expansion:

- The Edge AI accelerator market is experiencing rapid growth (38.9% CAGR).

- Projected to reach \$7.68 billion by 2027, indicating significant demand for on-device AI.

#### • Key Adoption Drivers:

- Driven primarily by the need for low latency (78.3% of organizations) for real-time responses.

- Data privacy concerns (64.7%) are also a major factor, favoring local processing.

#### • Industry Adapting to Challenges:

Widespread model optimization (used in 82% of deployments) shows the market actively working to run complex AI efficiently on constrained edge hardware.

### Hardware Acceleration Solutions

## Neural Processing Units

Dedicated AI accelerators in modern SoCs

- 10-15x energy efficiency vs. CPU

- Specialized for common neural net operations

#### **Edge TPUs**

Google's purpose-built edge accelerators

- 4 TOPS in small form factor

- 2 W power envelope

#### Mobile GPUs

Increasingly optimized for AI workloads

- Parallel processing capabilities

- Driver optimizations for neural networks

#### **FPGA Accelerators**

Reconfigurable hardware for custom workloads

- Adaptable to specific model architectures

- Power-efficient for production deployments

Specialized hardware accelerators dramatically improve the performance and energy efficiency of edge AI workloads. Modern system-on-chips (SoCs) increasingly incorporate neural processing units (NPUs) that deliver an order of magnitude better performance-per-watt compared to general-purpose CPUs.

These purpose-built accelerators are specifically designed to handle the computational patterns of neural networks, with optimized datapaths for matrix multiplication and activation functions that dominate AI workloads.

## Edge GPU's: Overview

Table 1: Comparative Specification Overview of Select Edge GPU/Accelerator Families

| Feature                       | NVIDIA<br>Jetson<br>Orin<br>Nano<br>Super<br>8GB | NVIDIA<br>Jetson<br>Orin NX<br>16GB | NVIDIA<br>Jetson<br>AGX<br>Orin<br>64GB | NVIDIA<br>RTX<br>4000<br>SFF Ada | AMD Ryzen<br>AI 300<br>Series<br>(Rep. NPU) <sup>1</sup> | Intel Core<br>Ultra (Rep.<br>NPU) <sup>2</sup> | Intel Arc<br>A380E     | Google<br>Coral<br>Dual<br>Edge TPU<br>M.2 | Qualcomm<br>Snapdragon<br>X Elite (Rep.<br>NPU) <sup>3</sup> | EdgeCortix<br>SAKURA-I |

|-------------------------------|--------------------------------------------------|-------------------------------------|-----------------------------------------|----------------------------------|----------------------------------------------------------|------------------------------------------------|------------------------|--------------------------------------------|--------------------------------------------------------------|------------------------|

| Manufacturer                  | NVIDIA                                           | NVIDIA                              | NVIDIA                                  | NVIDIA                           | AMD                                                      | Intel                                          | Intel                  | Google                                     | Qualcomm                                                     | EdgeCortix             |

| Key<br>Accelerator            | GPU +<br>Tensor<br>Cores                         | GPU +<br>Tensor<br>Cores            | GPU +<br>Tensor<br>Cores +<br>DLAs      | GPU +<br>Tensor<br>Cores         | NPU<br>(XDNA) +<br>iGPU<br>(RDNA)                        | NPU +<br>iGPU (Arc)                            | GPU<br>(Arc)           | TPU<br>(ASIC)                              | NPU<br>(Hexagon)                                             | DNA<br>(ASIC/FPGA)     |

| Al Perf.<br>(TOPS)            | 67 (INT8<br>Sparse)                              | 100-157<br>(INT8<br>Sparse)         | 275<br>(INT8<br>Sparse)                 | 19.2<br>TFLOPS<br>(FP32)         | ~45 TOPS<br>(Total<br>System)4                           | ~10-11<br>TOPS (NPU<br>only) <sup>5</sup>      | ~5<br>TFLOPS<br>(FP32) | 8 (INT8)                                   | 45 (NPU<br>only)⁵                                            | 40 (INT8<br>Dense)     |

| Memory<br>Capacity (GB)       | 8                                                | 16                                  | 64                                      | 20                               | System<br>RAM                                            | System<br>RAM                                  | 6<br>(GDDR6)           | N/A (Uses<br>Host)                         | System RAM                                                   | N/A (Uses<br>Host)     |

| Memory<br>Bandwidth<br>(GB/s) | 102                                              | 102.4                               | 204.8                                   | 160                              | LPDDR5X<br>(System)                                      | LPDDR5/x<br>(System)                           | 186                    | N/A                                        | 136<br>(LPDDR5X)                                             | N/A                    |

| TDP (W)                       | 7-25                                             | 10-25                               | 15-60                                   | 70                               | Laptop TDP                                               | Laptop<br>TDP                                  | 75                     | ~4<br>(Module)                             | Laptop TDP                                                   | 5-10                   |

| Typical Form<br>Factor        | SOM                                              | SOM                                 | SOM                                     | SFF PCle<br>Card                 | Integrated<br>SoC                                        | Integrated<br>SoC                              | PCle<br>Card           | M.2 E-Key                                  | Integrated<br>SoC                                            | PCIe Card /<br>Chip    |

|                               |                                                  |                                     |                                         |                                  |                                                          |                                                |                        |                                            |                                                              |                        |

## Edge GPU's: Inference Performace

| Table 2: LLM Inference Performance Comparisor | (Illustrative - Based on Fragmented Data) |

|-----------------------------------------------|-------------------------------------------|

|-----------------------------------------------|-------------------------------------------|

| Hardware                            | LLM Model              | Quantization    | Software/Framework              | Throughput<br>(Tokens/Sec) | Latency<br>(TTFT ms /<br>ITL ms) | Power<br>(W)  | Source/Notes                                                                                                |

|-------------------------------------|------------------------|-----------------|---------------------------------|----------------------------|----------------------------------|---------------|-------------------------------------------------------------------------------------------------------------|

| NVIDIA GPU<br>(RTX 4090)            | Mistral 7B             | INT4 (AWQ)      | TensorRT-LLM v0.7.1             | ~170                       | N/A / ~5.9                       | N/A           | Single user benchmark.<br>Significantly faster than<br>Ilama.cpp (~100 TPS) on same<br>HW.                  |

| NVIDIA GPU<br>(RTX 3090)            | Mistral 7B             | INT4 (AWQ)      | TensorRT-LLM v0.7.1             | ~142                       | N/A / ~7.0                       | N/A           | Single user benchmark. ~62% faster than llama.cpp (~87 TPS) on same HW.                                     |

| NVIDIA Jetson<br>Orin Nano<br>Super | Llama 3.1 8B           | Optimized       | TensorRT-LLM /<br>JetPack 6+    | Data Needed                | Data<br>Needed                   | 7-25W         | Capability confirmed,<br>performance claimed 1.7x<br>higher than Orin Nano. Specific<br>benchmarks pending. |

| NVIDIA Jetson<br>Orin NX 16GB       | Llama 2 7B<br>Chat     | GPTQ<br>(INT4?) | TensorRT-LLM v0.12<br>(Preview) | Data Needed                | Data<br>Needed                   | 10-25W        | Feasibility shown, requires<br>JetPack 6.1+. Specific<br>benchmarks pending.                                |

| AMD Ryzen AI<br>300 Series          | Llama 3.1 8B           | INT4 (W4A16)    | ONNX Runtime + Vitis<br>AI EP   | Data Needed                | Data<br>Needed                   | Laptop<br>TDP | Supported via LLM Hybrid OGA<br>flow (NPU+iGPU). Specific<br>performance data needed.                       |

| AMD Ryzen AI<br>300 Series          | Mistral 7B<br>Instruct | INT4 (W4A16)    | ONNX Runtime + Vitis<br>AI EP   | Data Needed                | Data<br>Needed                   | Laptop<br>TDP | Supported via LLM Hybrid OGA<br>flow (NPU+iGPU). Specific<br>performance data needed.                       |

| Intel Core Ultra<br>(NPU)           | Llama /<br>Mistral     | Optimized       | IPEX-LLM / OpenVINO             | Data Needed                | Data<br>Needed                   | Laptop<br>TDP | Experimental support exists.  Performance highly dependent on software maturity.                            |

| Intel Arc A770<br>(16GB)            | DeepSeek-<br>R1 67B    | Q4_K_M          | llama.cpp (via IPEX-<br>LLM)    | Data Needed                | Data<br>Needed                   | ~225W<br>TDP  | Feasibility shown for very large<br>models on desktop Arc GPU<br>with specific framework.                   |

| Mobile SoC<br>(Dimensity<br>9300)   | 7B Model               | N/A (FP16?)     | llama.cpp                       | -5x vs SD870<br>(decode)   | N/A                              | Mobile<br>TDP | Relative CPU performance<br>shown, not absolute<br>TPS/Latency on GPU/NPU.                                  |

## Beyond Physical Hardware

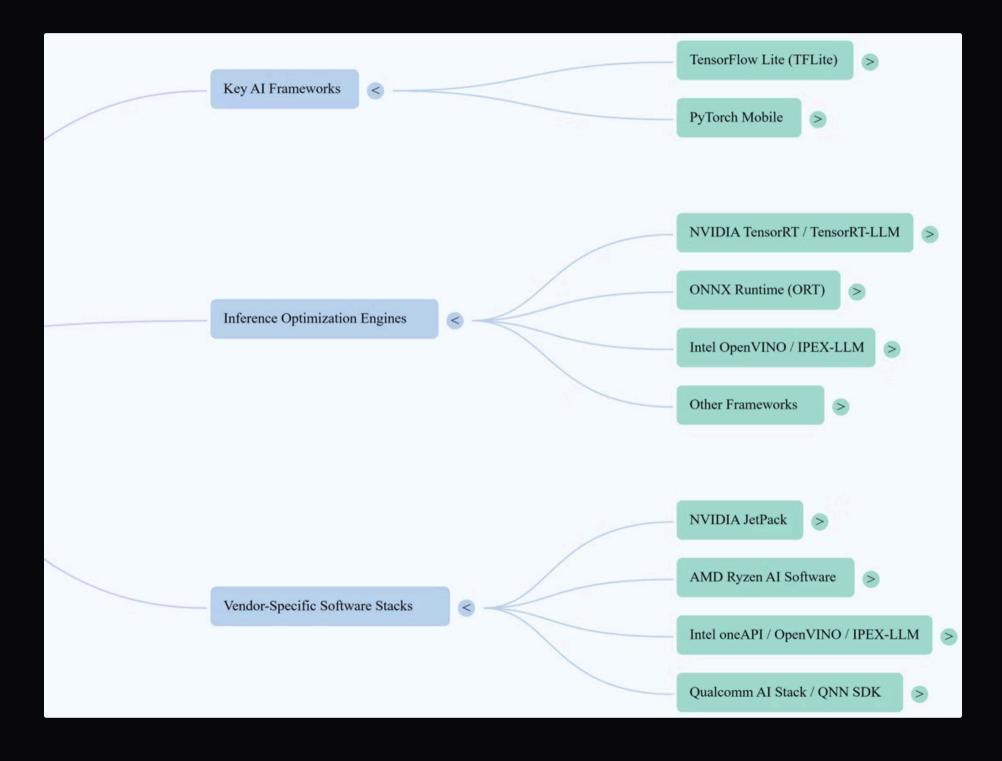

## Framework Implementation Options

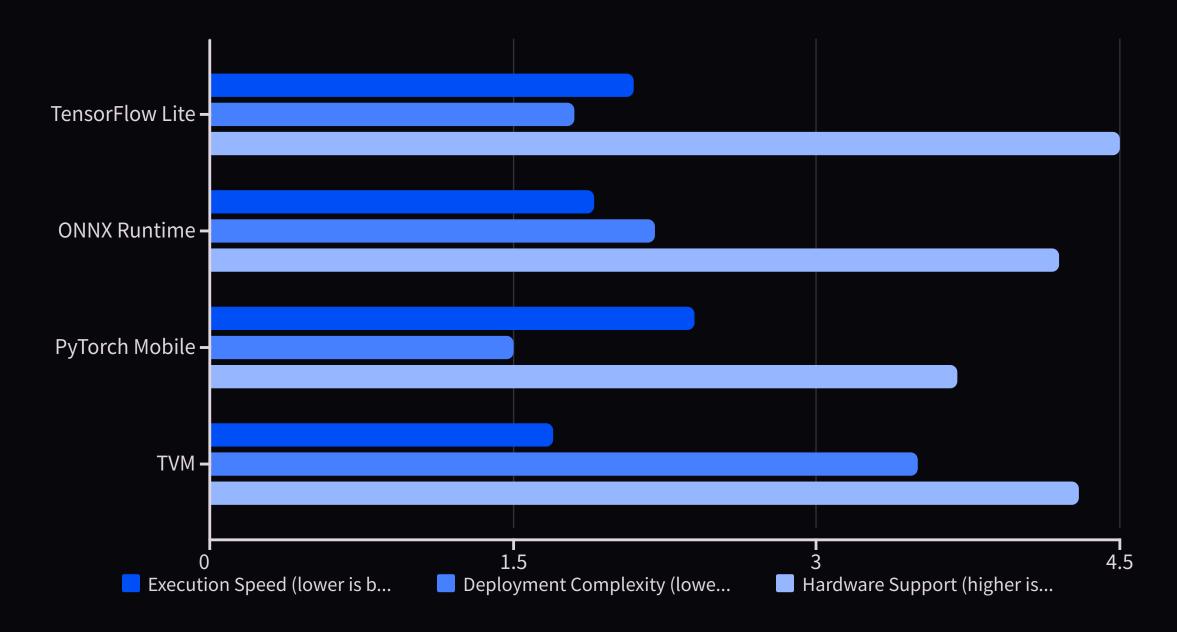

Selecting the appropriate framework for edge deployment is critical. TensorFlow Lite offers excellent hardware support through delegations to NPUs and GPUs, while ONNX Runtime provides superior cross-platform model portability and slightly better raw execution speed for many workloads.

PyTorch Mobile excels in developer experience and deployment simplicity, making it attractive for rapid prototyping. TVM offers the best performance through deep compiler optimizations but requires significantly more implementation complexity and expertise to fully leverage its capabilities.

## LLM Optimization Techniques

Key techniques to optimize large language models (LLMs) include:

- 1. Quantization (Most crucial technique)

- 2. Network Pruning

- 3. Knowledge Distillation

- 4. Low-Rank Approximation / Factorization

- 5. Memory Optimizations

Our talk will focus on the top 3 techniques in this list.

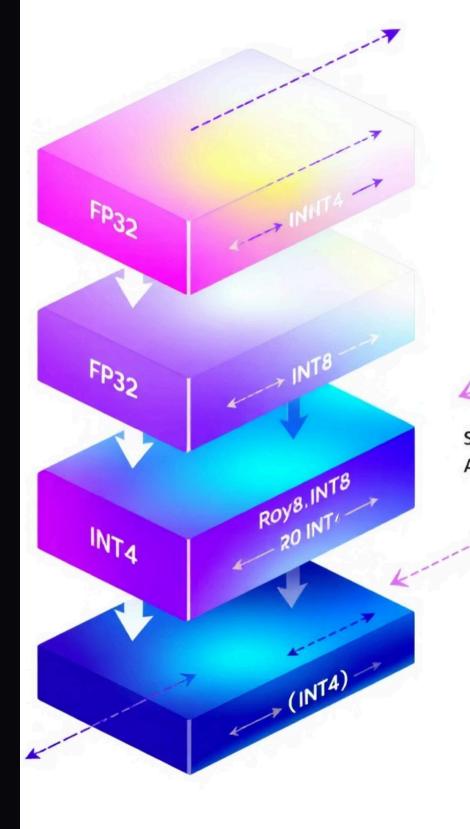

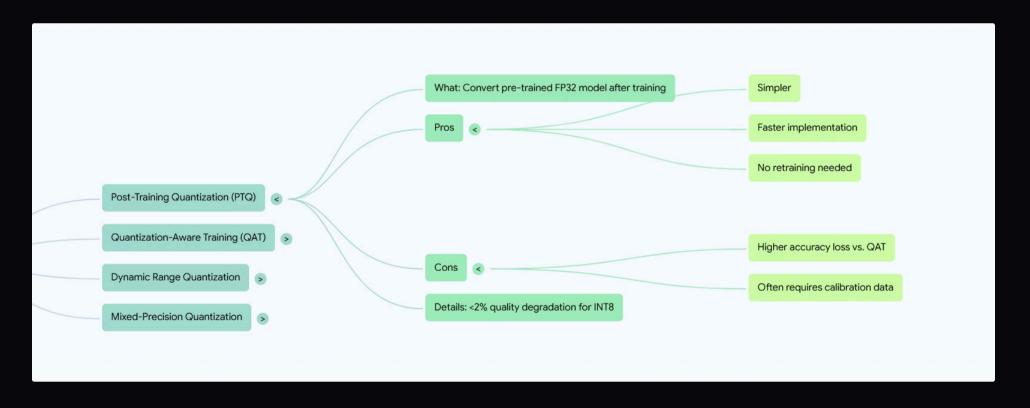

## Quantization Techniques

#### Post-Training Quantization

Converting pre-trained model weights from floating-point (FP32) to lower precision formats (INT8, INT4) after training completion.

- Minimal development effort

- No retraining required

- Moderate accuracy trade-off

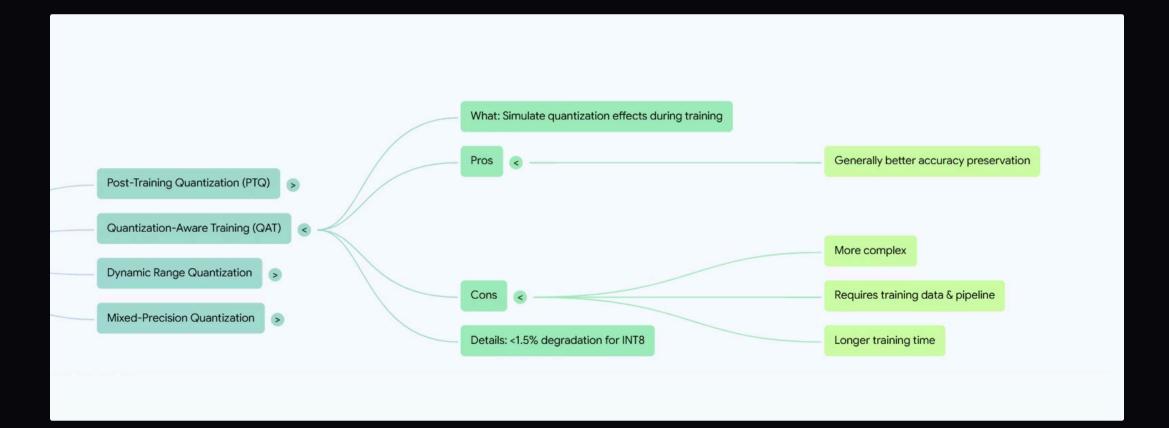

## **Quantization-Aware Training**

Incorporating quantization effects during the training process to minimize accuracy loss when deploying with reduced precision.

- Higher implementation complexity

- Better accuracy preservation

- Model learns to compensate for quantization artifacts

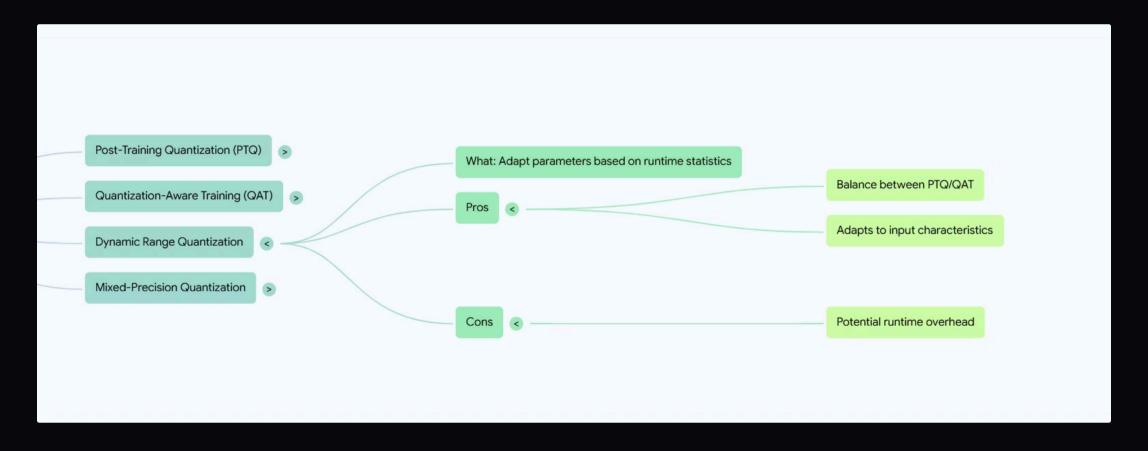

## Dynamic Range Quantization

Adaptively adjusting quantization parameters based on the statistical properties of activations during inference.

- Balances accuracy and performance

- Adapts to input characteristics

- Lower memory bandwidth requirements

## Precision-Aware Quantization

## Post-Training Quantization

Simple conversion from FP32 to INT8/INT4 after training is complete. Minimal accuracy loss for many models.

## Quantization-Aware Training

Incorporates quantization effects during training process. Models learn to compensate for reduced precision.

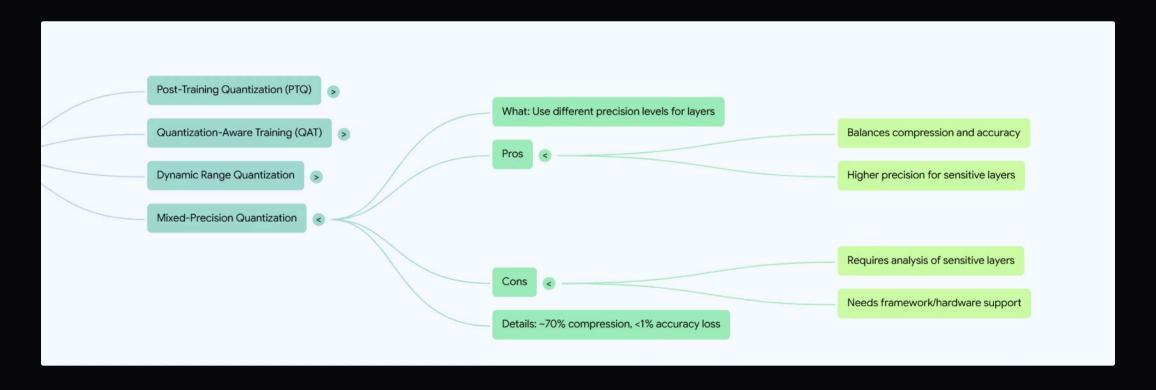

#### **Mixed-Precision Deployment**

Different precision for different layers based on sensitivity analysis. Critical layers may retain higher precision.

Quantization dramatically reduces the computational and memory requirements of neural networks by representing weights and activations at lower precision. Converting from 32-bit floating point to 8-bit integer can yield 4x smaller models with 3-4x faster inference.

Advanced techniques like mixed-precision quantization allow for targeted optimization, preserving full precision only where absolutely necessary while aggressively quantizing less sensitive network components.

## Quantization Technique: PTQ

## GPU requirements for Float32 vs Int8 Weights

#### **NVIDIA A10**

Accelerated Graphics and Video with Al for Mainstream Enterprise Servers

#### Enrich Graphics and Video Applications with Powerful Al

The NVIDIA A10 Tensor Core GPU combines with NVIDIA RTX Virtual Workstation (vWS) software to bring mainstream graphics and video with AI services to mainstream enterprise servers, delivering the solutions that designers, engineers, artists, and scientists need to meet today's challenges. Built on the latest NVIDIA Ampere architecture, the A10 combines second-generation RT Cores, third-generation Tensor Cores, and new streaming microprocessors with 24 gigabytes (GB) of GDDR6 memory—all in a 150W power envelope—for versatile graphics, rendering, AI, and compute performance. From virtual workstations, accessible anywhere in the world, to render nodes to the data centers running a variety of workloads, A10 is built to deliver optimal performance in a single-wide, full-height, full-length PCIe form factor.

NVIDIA A10 is supported as part of NVIDIA-Certified Systems<sup>™</sup>, in the onprem data center, in the cloud, and at the edge. NVIDIA A10 builds on the rich ecosystem of AI frameworks from the NVIDIA NGC<sup>™</sup> catalog, CUDA-X<sup>™</sup> libraries, over 2.3 million developers, and over 1,800 GPU-optimized applications to help enterprises solve the most critical challenges in their business.

#### **SPECIFICATIONS**

| FP32                  | 31.2 TF                                                       |  |  |  |

|-----------------------|---------------------------------------------------------------|--|--|--|

| TF32 Tensor Core      | 62.5 TF   125 TF*                                             |  |  |  |

| BFLOAT16 Tensor Core  | 125 TF   250 TF*                                              |  |  |  |

| FP16 Tensor Core      | 125 TF   250 TF*                                              |  |  |  |

| INT8 Tensor Core      | 250 TOPS   500 TOPS*                                          |  |  |  |

| NT4 Tensor Core       | 500 TOPS   1000 TOPS*                                         |  |  |  |

| RT Cores              | 72                                                            |  |  |  |

| Encode / Decode       | 1 encoder<br>2 decoders<br>(+AV1 decode)                      |  |  |  |

| GPU Memory            | 24 GB GDDR6                                                   |  |  |  |

| GPU Memory Bandwidth  | 600 GB/s                                                      |  |  |  |

| nterconnect           | PCIe Gen4: 64 GB/s                                            |  |  |  |

| Form Factor           | 1-slot FHFL                                                   |  |  |  |

| Max TDP Power         | 150W                                                          |  |  |  |

| vGPU Software Support | NVIDIA vPC/vApps,<br>NVIDIA RTX™ vWS,<br>NVIDIA AI Enterprise |  |  |  |

| Secure and Measured   | Yes (optional)                                                |  |  |  |

## Quantization Technique: QAT

## Quantization Technique: Dynamic Range

## Quantization Technique: Mixed Precision

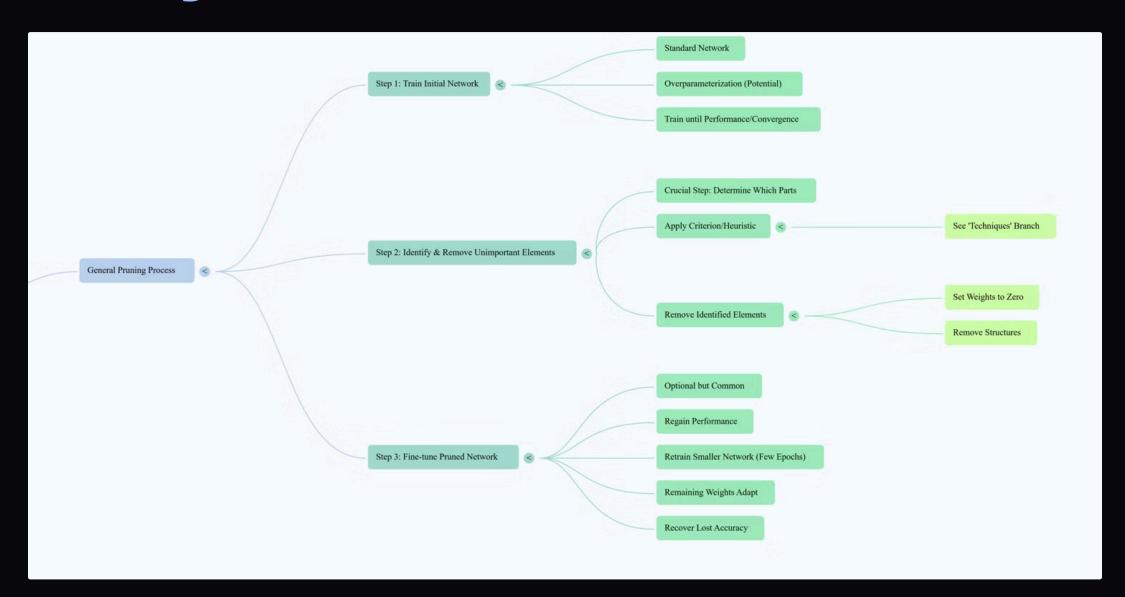

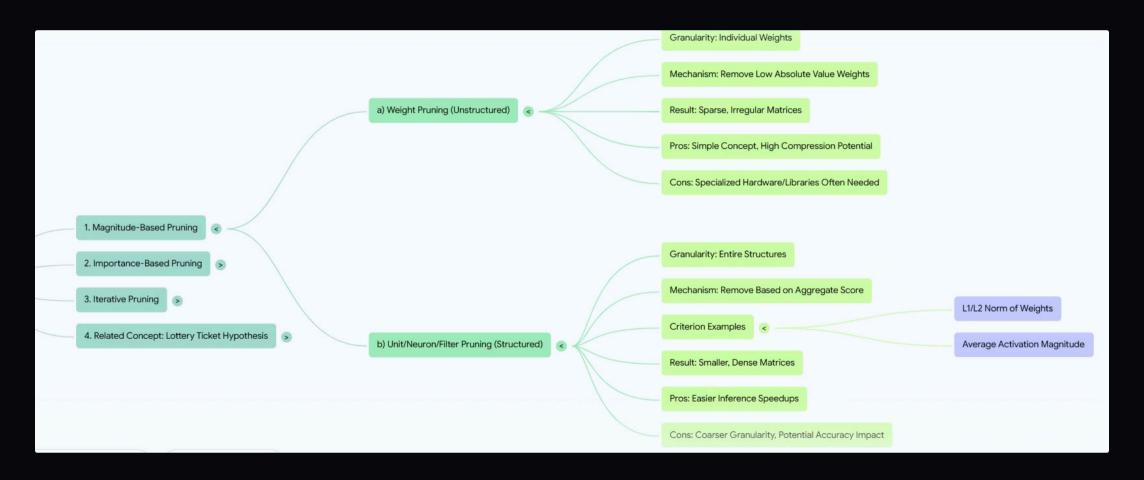

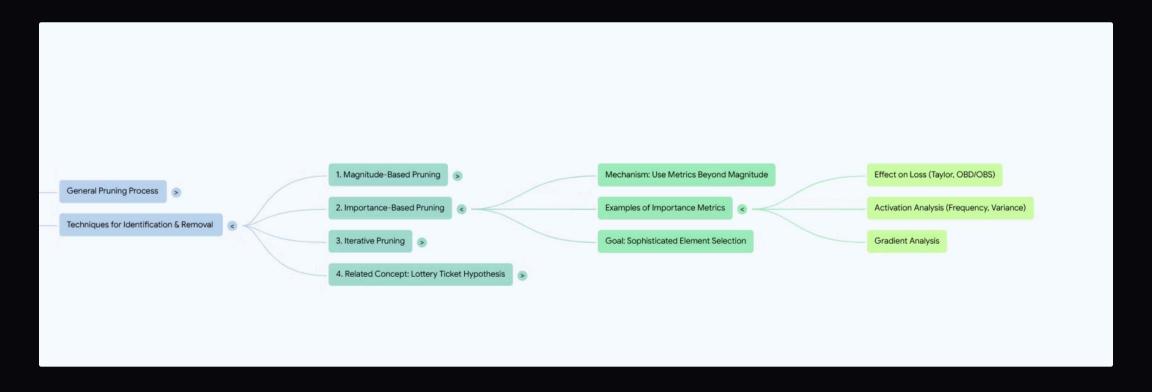

## Neural Network Pruning Techniques

#### **Identify Redundancy**

Analyze weight distributions and activation patterns to locate non-essential parameters

#### **Structured Pruning**

Remove entire filters, channels, or neurons for hardware compatibility

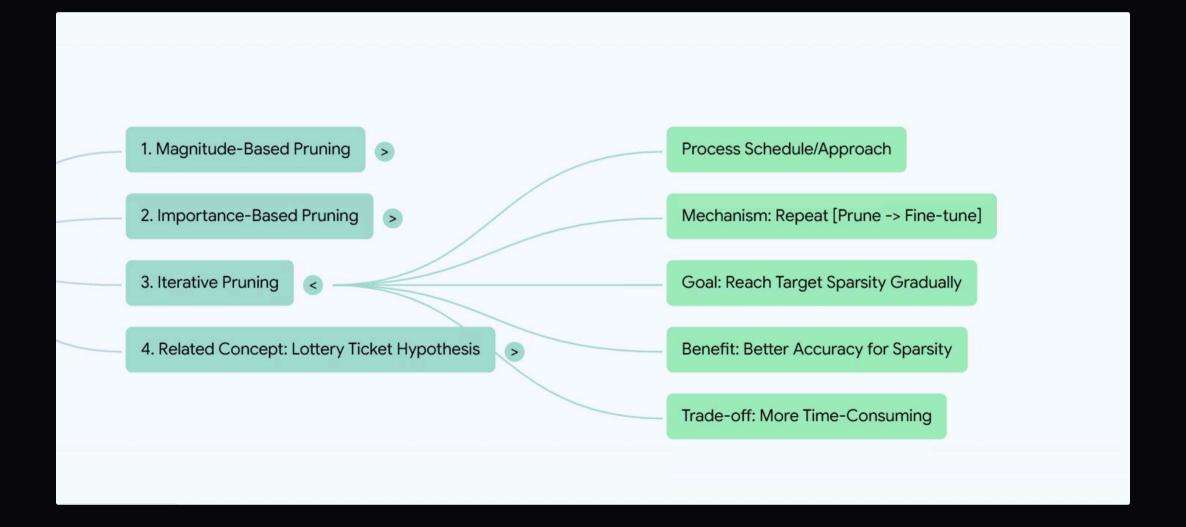

#### **Iterative Magnitude Pruning**

Gradually remove small weights while retraining to maintain accuracy

#### Sensitivity Analysis

Evaluate impact of pruning on overall model performance

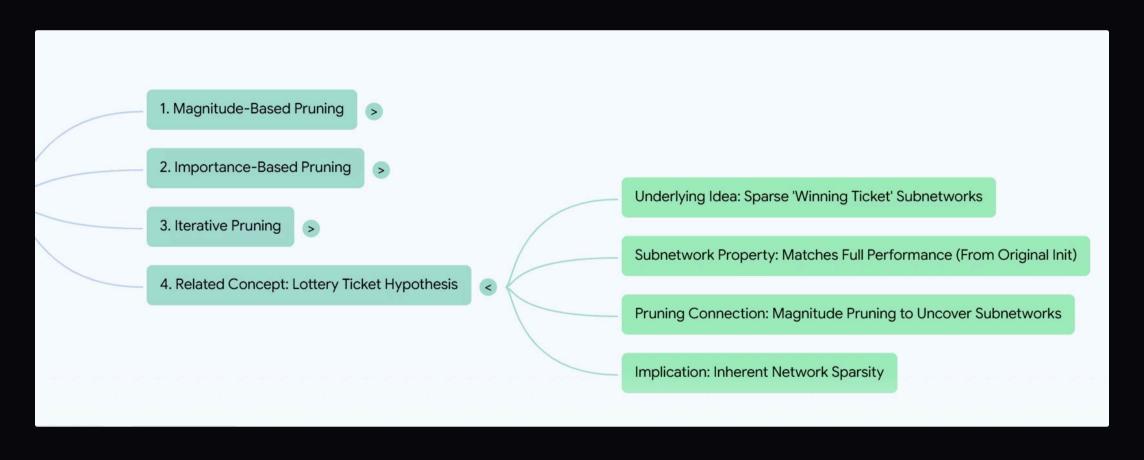

Targeted pruning can reduce model footprints by 50-90% with minimal accuracy impact. By systematically eliminating redundant parameters, we create leaner networks that maintain essential performance characteristics while requiring significantly fewer computational resources.

Our research shows that iterative pruning combined with fine-tuning yields the best results, allowing models to adapt to their reduced parameter space while preserving critical functional pathways.

## **Pruning Process**

## Pruning Technique: Magnitude-Based

## Pruning Technique: Importance-Based

## Pruning Technique: Iterative-Based

## Pruning Technique: Lottery Ticket Hypothesis

### **Knowledge Distillation for Edge**

Knowledge distillation accelerates inference by transferring capabilities from comprehensive teacher models to lightweight student models engineered specifically for edge environments. This approach allows small models to benefit from the learning of much larger networks.

Rather than simply training on hard labels, student models learn from the probability distributions of teacher models, capturing nuanced relationships between classes and enabling better generalization despite their reduced capacity.

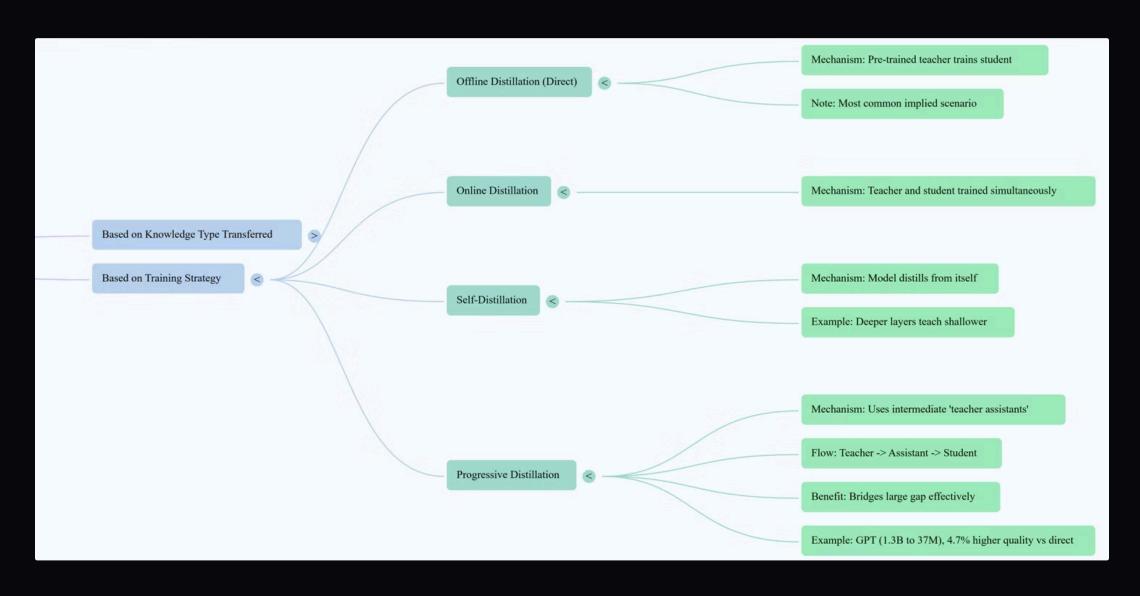

## Knowledge Distillation: Based on Type Transferred

## Knowledge Distillation: Based on Training Strategy

## Edge-Optimized Model Architectures

#### **MobileNets**

Depthwise separable convolutions reduce computation by 8-9x while maintaining reasonable accuracy for vision tasks.

#### ShuffleNet

Channel shuffling and grouped convolutions optimize for devices with limited computing resources.

#### SqueezeNet

Fire modules with squeeze layers reduce parameter count while preserving performance on classification tasks.

#### **EfficientNet**

Compound scaling method optimizes width, depth, and resolution for superior efficiency-accuracy tradeoff.

Purpose-built architectures designed specifically for resource-constrained environments deliver substantially better performance than simply shrinking standard models. These specialized architectures incorporate operations like depthwise separable convolutions that dramatically reduce computational requirements.

The latest generation of edge-optimized models achieves performance approaching that of models 5-10x their size through architectural innovations rather than simply scaling down existing designs.

### Case Study: Edge Voice Assistant

98.2%

87.3%

Wake Word Accuracy

False activation rate below 0.5%

**Command Recognition**

Across various acoustic environments

**76MB**

**Model Size**

Full wake+command system footprint

85ms

**Response Latency**

End-to-end processing time

Our edge-deployed voice assistant demonstrates how optimization techniques deliver compelling real-world performance. Using a combination of neural network pruning and 8-bit quantization, we reduced the model footprint by 73% compared to the baseline while maintaining excellent accuracy.

Knowledge distillation from a larger teacher model enabled our compact architecture to achieve wake word detection accuracy of 98.2% with a false activation rate below 0.5%. The entire system operates with an end-to-end latency of 85ms, well below the 100ms threshold for perceived real-time interaction.

## Key Takeaways & Implementation Roadmap

#### Establish Performance Targets

Define clear latency, accuracy, and resource budgets for your edge AI application. Consider both average and worst-case scenarios.

## Apply Integrated Optimization

Combine pruning, quantization, and distillation techniques rather than relying on a single approach. The compound effect delivers significantly better results.

## Test on Target Hardware

Benchmark on actual deployment devices, as emulators often miss critical performance characteristics. Profile to identify bottlenecks.

#### Iterate with Real-World Data

Continuously refine your models based on edge-collected data to adapt to deployment conditions not seen during initial training.

Successfully deploying GenAI at the edge requires a systematic approach that considers the entire optimization pipeline. By leveraging the techniques presented today, you can achieve breakthrough performance metrics on resource-constrained devices.

Remember that edge AI optimization is an iterative process. Start with establishing clear performance targets, apply integrated optimization techniques, thoroughly test on target hardware, and continuously refine your models with real-world data. This methodical approach will help you navigate the unique challenges of edge AI development.

### Benchmarking for Consistent Performance

#### **Define Metrics**

Establish key performance indicators including latency, throughput, accuracy, and energy consumption

Use benchmark results to guide further refinements of model architecture and parameters

#### **Test Environment**

Create standardized testing procedures that simulate real-world deployment conditions

#### Measure Performance

Collect comprehensive metrics across different hardware targets and workloads

Systematic benchmarking is essential for validating optimization results and ensuring consistent performance across diverse deployment scenarios. Our framework includes tools for automated testing across multiple hardware targets and operating conditions.

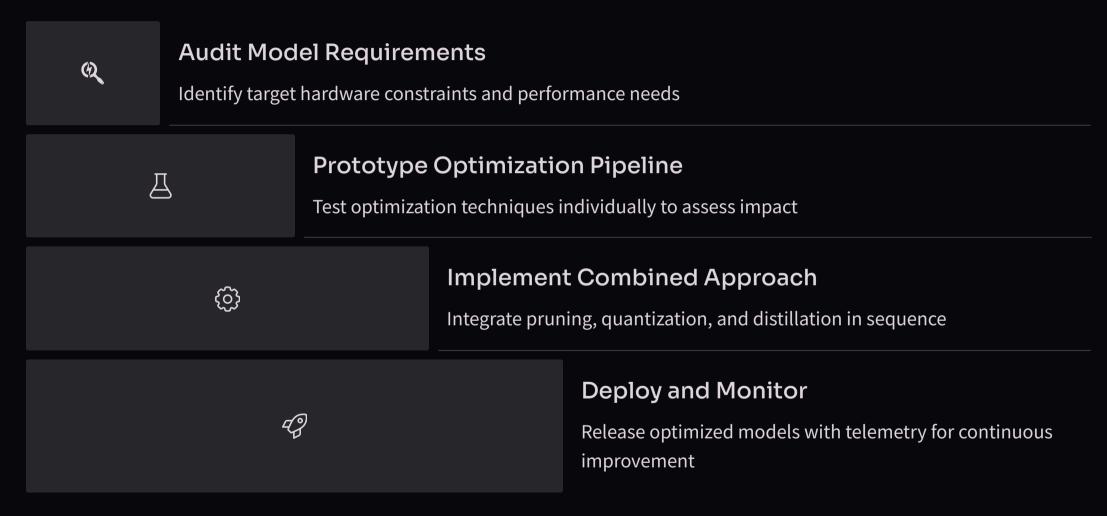

### Implementation Roadmap

Start your edge AI optimization journey with a comprehensive audit of your model requirements and hardware constraints. Develop a systematic pipeline that combines multiple optimization techniques, with careful validation at each stage. Implement a monitoring system after deployment to gather real-world performance data and guide future improvements.

## Thank you